e-ISSN: 2319-8753 | p-ISSN: 2347-6710

TEDIA

International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 12, Issue 6, June 2023

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

## Impact Factor: 8.423

9940 572 462

6381 907 438

$\bigcirc$

e-ISSN: 2319-8753, p-ISSN: 2320-6710 www.ijirset.com | Impact Factor: 8.423 A Monthly Peer Reviewed & Referred Journal |

Volume 12, Issue 6, June 2023

| DOI:10.15680/IJIRSET.2023.1206083 |

## Performance Analysis of 5-Level Diode Clamp Single Phase Inverter

#### <sup>1</sup>Vivek Kumar, <sup>2</sup>Prof. Amit Kumar Namdev

M. Tech Scholar, Department of Electrical Engineering, Mittal Institute of Technology, Bhopal (M.P.), India<sup>1</sup> Head of Dept., Department of Electrical Engineering, Mittal Institute of Technology, Bhopal (M.P.), India<sup>2</sup>

**ABSTRACT:** Multilevel inverters (MLIs) have been widely accepted as a potential solution for high-efficiency electric power-electronic conversion systems by both research and industry community. The inherent features of MLIs like reduced dv/dt, high-quality output waveform, lower switching frequency, etc., are the key reasons for the usage of MLIs in a variety of fields including motor drives, renewable energy sources integration, locomotives, to name a few. Renewable energy sources use to generate green energy for reduce environment pollution problem. In this paper build a PV system that is transmit a power to the grid. A grid connected photovoltaic system is becoming increasingly important for the solution in renewable energy. Various types of inverter have been proposed for PV grid connected application such as multilevel inverters, current source inverter, voltage source inverter and etc. In this block diagram shows PV to grid connected system. This work processed in two stage where, stage one is the DC-DC boost converter with MPPT (Maximum power point) tracking and second stage is the five-level inverter. For this stage levelled output passes through designed LCL filter which gives AC output and connected to grid. Its achieves a minimum value of the THD i.e., 0.46% that is good enough to use for the grid and also can be used for the different load applications.

#### KEYWORDS: Multi-level Inverter, 13-level, PWM, Boost Factor

#### I. INTRODUCTION

In modern technology, power electronics and processor plays a vital role in the field of motor control, light control, heat control, power supplies, vehicle system, HVDC, FACTS and renewable applications. The philosophy focuses on preserving the energy and meeting the power demand accurately and the power modulator pertaining to inverter / converter technology fulfills the requirements and this attracts the researchers to explore in the inverter field. The above-mentioned applications work in the range of medium power, high power at a higher voltage. With the help of semiconductor device technology, power converters are to be designed with higher operating voltage. As a single device fails to support such high voltages, a number of devices need to connect in series to meet the voltage rating. Another challenge in the industrial sector is the requirement and maintenance of the sinusoidal power supply with variable voltage and frequency. The above demerits are overcome by the introduction of Inverters. The series connected switches in the inverters and through control mechanism, the voltage stress with respect to high voltage rating is shared among the series switches and also the losses are minimized. Due to advantage of minimum losses, inverters is also used for medium voltage applications. The classical square wave inverter operating at higher voltage introduces the dominant harmonics, thereby the performance on the load side and on the front end of the inverter has a large impact and the performance is affected. Though the solution is sought through the passive filters, the loss are increased and occupies more space. The alternative path is provided by Multilevel Inverters (MLI) [1, 2]. MLI generates sinusoidal voltage waveform in the form voltage steps through switching sequence. The other advantages of MLI are reduced electromagnetic interference, reduced current distortion, good quality voltage waveform, good current waveform. The basic types of MLI are neutral point clamped MLI, flying capacitor MLI and cascaded H- bridge MLI. To synthesize nearly sinusoidal voltage, higher number of levels needs to be generated with the help of more number of switches, more number of sources and more number of gate drivers [3, 4]. Due to this, the efficiency decreases as more number of switches is utilized in the conduction path.

#### II. MULTI LEVEL INVERTER TOPOLOGIES

The conventional single phase inverter suffers from a drawback of higher THD. Hence, it is not suited for grid connected applications. MLIs have many advantages for medium and high power systems as they synthesis a higher output voltage rating of each switching device. Stepped output voltage allows a reduction in harmonic content of

よう は IJIRSET |e-ISSN: 2319-8753, p-ISSN: 2320-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

Volume 12, Issue 6, June 2023

#### DOI:10.15680/IJIRSET.2023.1206083

voltage and current waveforms, switching frequency and semiconductor voltage level. The presented merits make MLIS appropriate for RE applications. The best well known multilevel inverter topologies are diode clamped, flying capacitor and cascaded MLIS [5, 6].

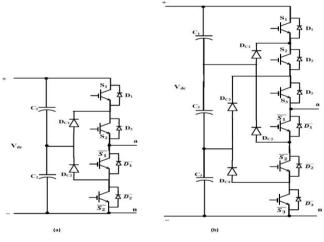

#### 2.1 Diode Clamped Multilevel Inverter

Concept of the diode clamped topology was proposed by Nabae et al 1981. This topology has found wide acceptance for its capability of higher voltages and high efficiency operation. A phase leg of a three-level diode clamped inverter is shown in Figure 1(a). It consists of two pairs of switches and diodes. Each switching pairs works in complementary mode and the diodes are used to provide access to mid-point voltage. The DC bus voltage is split into three voltage levels by using two series connection of DC capacitors, C1 and C2. Each capacitor is supposed to have an equal DC voltage and each voltage stress will be limited to one capacitor level through clamping diodes (DC1 and DC2). If assumed that total DC link voltage is Vdc and mid-point is regulated to half of the DC link voltage, the voltage across each capacitor is Vdc/ 2 (VC1 = VC2 = Vdc/2). Based on the structure of the diode clamped inverter, there are three different possible switching states which apply the staircase voltage on output voltage relating to DC link capacitor voltage rate. Switching states of the three level inverter are summarized in Table 1.

To study the effect of the number of output voltage levels in diode clamped topology, Figure 1(b) shows a phase leg of a four-level inverter. If converter works in balance condition, DC link voltage split into three different values by the series capacitor (VC1 = VC2 = VC3 = Vdc/3).

Figure 1: One leg of diode clamped inverter (a) three-level (b) four level

| Table 1. Switching | states in one | leg of the | three-level | diode clamped inverter | , |

|--------------------|---------------|------------|-------------|------------------------|---|

| rable r. Switching | states in one | leg of the | unce-iever  | uloue clamped inverter |   |

| S1  | <b>S</b> <sub>2</sub> | Leg Voltage (Van)  |

|-----|-----------------------|--------------------|

| ON  | ON                    | V <sub>dc</sub>    |

| OFF | ON                    | V <sub>dc</sub> /2 |

| OFF | OFF                   | 0                  |

#### **III. PROPOSED METHODOLOGY**

Representation of this work using block diagram which is shown in figure 2

Figure 2: Representation of PV energy to grid connected system

よう縁 IJIRSET

|| Volume 12, Issue 6, June 2023 ||

e-ISSN: 2319-8753, p-ISSN: 2320-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

#### | DOI:10.15680/IJIRSET.2023.1206083 |

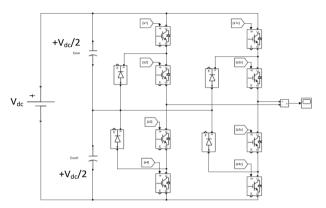

#### **Designing of 5-Level Inverter**

In this work proposed a novel 5 level inverter which is suitable to connect PV and transmit a power to the grid. Proposed inverter generates a five level at the output of the inverter as  $V_{dc}$ ,  $V_{dc}/2$ , 0,  $-V_{dc}/2$ ,  $V_{dc}$ . Proposed topology is represented in figure 3. This topology has 8 unidirectional switches and 4 diodes and it have 2 capacitors as a dc-bus capacitor which is connected after the first stage which is DC-DC boost converter. Levelled voltage as a five-level voltage occurs at the output of the inverter.

Figure 3: Proposed five level topologies

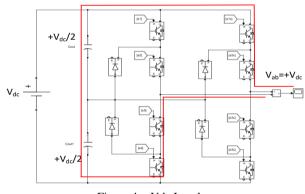

Figure 4: +Vdc Level

By turning ON switch S3, S4, S1c and S2c and other switch OFF, capacitors C1 and C2 are connected in series through the load and it gives +Vdc voltage at the output of inverter. This stage specified in Figure 4.

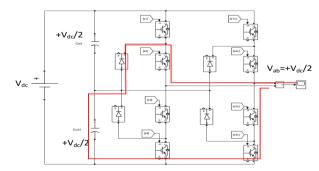

#### +Vdc/2 Level

+Vdc level

By turning ON switch S2, S3c and S4c and other switch OFF, capacitors C2 is connected in series through the load and C1 is by passed and it gives +Vdc/2 voltage at the output of inverter. This stage specified in Figure 5.

Figure 5: +Vdc/2 Level

よう縁 IJIRSET |e-ISSN: 2319-8753, p-ISSN: 2320-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

|| Volume 12, Issue 6, June 2023 ||

#### | DOI:10.15680/IJIRSET.2023.1206083 |

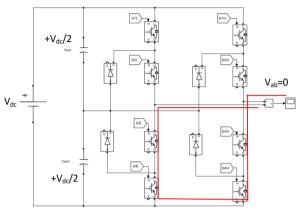

#### 0 Level

By turning ON switch S3, S4, S3c and S4c and other switch OFF, capacitors C1 and C2 are by passed and it gives 0 voltage at the output of inverter. This stage specified in Figure 6.

Figure 6: 0 Level

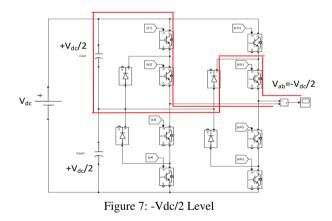

#### -Vdc/2 Level

By turning ON switch S1, S2 and S2c and other switch OFF, capacitors C1 is connected in series through the load and C2 is by passed and it gives -Vdc/2 voltage at the output of inverter. This stage specified in Figure 7.

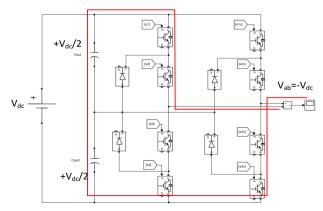

#### -Vdc Level

By turning ON switch S1, S2, S3c and S4c and other switch OFF, capacitors C1 and C2 are connected in series through the load and it gives -Vdc voltage at the output of inverter. This stage specified in Figure 8.

Figure 8: -Vdc Level

|e-ISSN: 2319-8753, p-ISSN: 2320-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

#### Volume 12, Issue 6, June 2023

#### | DOI:10.15680/IJIRSET.2023.1206083 |

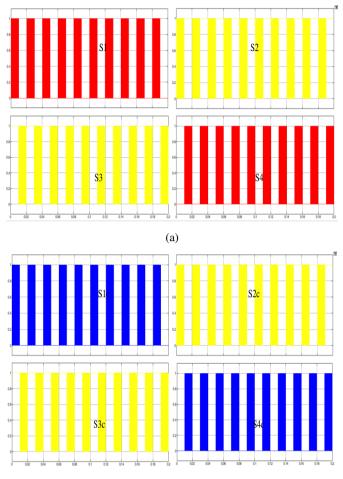

Generation of PWM signal for the proposed converter is described in Table 2.

| _ | Tuble 2: 5 witching States of the Hoposed 5 Elever Converter |               |    |    |            |    |     |     |     |     |

|---|--------------------------------------------------------------|---------------|----|----|------------|----|-----|-----|-----|-----|

|   | State                                                        | Voltage Level | S1 | S2 | <b>S</b> 3 | S4 | S1c | S2c | S3c | S4c |

|   | 1                                                            | +Vdc          | 0  | 0  | 1          | 1  | 1   | 1   | 0   | 0   |

|   | 2                                                            | +Vdc/2        | 0  | 1  | 0          | 0  | 0   | 0   | 1   | 1   |

|   | 3                                                            | 0             | 0  | 0  | 1          | 1  | 0   | 0   | 1   | 1   |

|   | 4                                                            | -Vdc/2        | 1  | 1  | 0          | 0  | 0   | 1   | 0   | 0   |

|   | 5                                                            | -Vdc          | 1  | 1  | 0          | 0  | 0   | 0   | 1   | 1   |

Table 2: Switching States of the Proposed 5-Level Converter

#### **IV. SIMULATION RESULT**

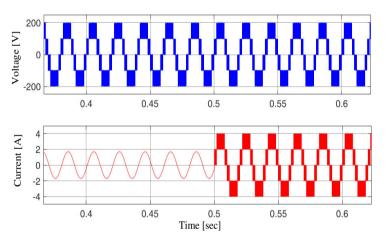

Figure 9 shows the dynamic response of the proposed multilevel inverter. In this intense the inductive load changes from 1000hm 200mH to 500hm 100mH at the time of 0.5sec. It can be clearly seen that the output voltage has not change at this time but output current has been doubled at this point. Its changes from 1.5A to the 3A after doing half of the inductive load.

Figure 10 shows the dynamic response of the proposed multilevel inverter. In this intense the inductive load change from 1000hm 100mH to pure resistive load 500hm at the time of 0.5sec. It can be clearly seen that the output voltage has not change at this time but output current has been doubled at this point. Its changes from 1.8A inductive current to the 4A resistive current after doing change the load.

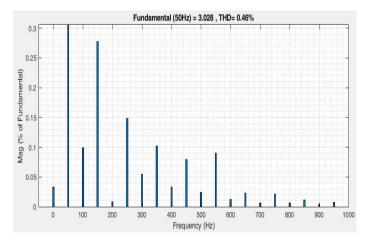

Figure 11 shows the Total harmonic profile (THD) of the output current. Its achieves a minimum value of the THD i.e., 0.46% that is good enough to use for the grid and also can be used for the different load applications. Figure 11 shows the PWM pulses across the switches.

Figure 9: Output voltage and current with inductive load change to resistive load

Figure 10: Total harmonic distortion (THD) profile of output current

e-ISSN: 2319-8753, p-ISSN: 2320-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

Volume 12, Issue 6, June 2023

#### DOI:10.15680/IJIRSET.2023.1206083

Figure 11: PWM snitching gate signals

#### V. CONCLUSION

Multilevel converters can operate at both fundamental switching frequency and high switching frequency PWM. It should be noted that the lower switching frequency usually means lower switching loss and higher efficiency. Hence, switching and conduction losses of the proposed inverter will be very less when compared to the other type of topologies.

In this intense the inductive load change from 1000hm 200mH to 500hm 100mH at the time of 0.5sec. It can be clearly seen that the output voltage has not change at this time but output current has been doubled at this point. Its changes from 1.5A to the 3A after doing half of the inductive load.

In this intense the inductive load change from 1000hm 100mH to pure resistive load 500hm at the time of 0.5sec. It can be clearly seen that the output voltage has not change at this time but output current has been doubled at this point. Its changes from 1.8A inductive current to the 4A resistive current after doing change the load. Its achieves a minimum value of the THD i.e., 0.46% that is good enough to use for the grid and also can be used for the different load applications. Figure 5.8 shows the PWM pulses across the switches.

#### REFRENCES

- [1] Sen, P.; Jha, V.; Sahoo, A.K., "Inrush current minimization in reduced device count multilevel inverter interfacing PV system", In Proceedings of the IEEE International Conference on Energy, Power and Environment: Towards Clean Energy Technologies, Shillong, Meghalaya, India, pp. 1–6, 2021.

- [2] Choi, U.-M.; Lee, J.-S., "Single-phase five-level IT-type NPC inverter with improved efficiency and reliability in photovoltaic systems", IEEE J. Emerg. Sel. Top. Power Electron, vol. 10, pp. 5226–5239, 2022.

- [3] Lee, S.S.; Yang, Y.; Siwakoti, Y.P., "A novel single-stage five-level common-ground-boost-type active neutral-point-clamped 5L-CGBT-ANPC inverter", IEEE Trans. Power Electron, vol. 36, pp. 6192–6196, 2021.

|e-ISSN: 2319-8753, p-ISSN: 2320-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

Volume 12, Issue 6, June 2023

#### | DOI:10.15680/IJIRSET.2023.1206083 |

- [4] Zhang, L.; Lou, X.; Li, C.; Wu, F.; Gu, Y.; Chen, G.; Xu, D. Evaluation of different Si SiC hybrid three-level active NPC inverters for high power density. IEEE Trans. Power Electron, vol. 35, pp. 8224–8236, 2020.

- [5] M. J. Sathik, N. Sandeep, D. Almakhles, and F. Blaabjerg, "Cross connected compact switched-capacitor multilevel inverter (c3-scmli) topology with reduced switch count," IEEE Transactions on Circuits and Systems II: Express Briefs, pp. 1–1, 2020.

- [6] J. Zeng, W. Lin, D. Cen and J. Liu, "Novel K-Type Multilevel Inverter With Reduced Components and Self-Balance," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 8, no. 4, pp. 4343-4354, 2020.

- [7] J. Zeng, W. Lin, D. Cen, and L. Junfeng, "Novel k-type multilevel inverter with reduced components and selfbalance," IEEE Journal of Emerging and Selected Topics in Power Electronics, 2019.

- [8] N. Sandeep and U. R. Yaragatti, "Design and implementation of active neutral-point-clamped nine-level reduced device count inverter: an application to grid integrated renewable energy sources," IET Power Electron., vol. 11, no. 1, pp. 82–91, 2017.

- [9] A. Taghvaie, J. Adabi, and M. Rezanejad, "A self-balanced step-up multilevel inverter based on switchedcapacitor structure," IEEE Trans. Power Electron., vol. 33, no. 1, pp. 199–209, 2017.

- [10] N. Sandeep and R. Y. Udaykumar, "Design and implementation of a sensorless multilevel inverter with reduced part count," IEEE Trans. Power Electron., vol. 32, no. 9, pp. 6677–6683, 2017.

- [11] M. Forouzesh, Y. P. Siwakoti, S. A. Gorji, F. Blaabjerg, and B. Lehman, "Step-up dc-dc converters: a comprehensive review of voltage-boosting techniques, topologies, and applications," IEEE Trans. Power Electron., vol. 32, no. 12, pp. 9143–9178, 2017.

- [12] E. Samadaei, S. A. Gholamian, A. Sheikholeslami, and J. Adabi, "An envelope type (e-type) module: asymmetric multilevel inverters with reduced components," IEEE Trans. Ind. Electron., vol. 63, no. 11, pp. 7148–7156, 2016.

- [13] Anjali Krishna, R.; Suresh, L.P. A brief review on multilevel inverter topologies. In Proceedings of the International Conference on Circuit, Power and Computing Technologies (ICCPCT), pp. 1–6, 2016.

- [14] Arbune, P.A.; Gaikwad, A., "Comparative study of three level and five level inverter", Int. J. Adv. Res. Electr. Electron. Instrum. Eng., vol. 5, pp. 681–686, 2016.

- [15] Y. Yu G. Konstantinou B. Hredzak and V. G. Agelidis "Power balance of cascaded H-bridge multilevel converters for large-scale photovoltaic integration" IEEE Trans. Power Electron., vol. 31, no. 1, pp. 292-303, 2016.

Impact Factor: 8.423

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com